КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Арифметико-логічні пристрої

|

|

|

|

Пристрої обробки інформації завжди містять операційний блок, що складається з послідовної і комбінаційної частин. Комбінаційна частина виконує арифметичні і логічні операції над двома багаторозрядними словами і тому складається із суматора, схеми порівняння й інших схем, що роблять різні логічні операції. Однак на практиці доцільніше використовувати спеціальний арифметико-логічний пристрій,який міг би здїйснювати всі необхідні операції і був би виконаний у виді однієї мікросхеми. Ці мікpocxеми виконують арифметичні і логічні перетворення двійкової інформації відповідно до програми на входах і в порівнянні з пристроями, що працюють по жорсткій наперед заданій програмі, являють собою пристрої більш високого класу. Ці мікросхеми так і називаються -арифметико-логічними пристроями (АЛП). У мікропроцесорній техніці AЛП є базовими елементами. Вони використовуються в сполученні з регістрами зсуву, оперативними пристроями й іншими вузлами. Мікросхеми AЛП входять до скдаду різних серій (наприклад, К155ІПЗ, КР531ІПЗ, К555ІПЗ, І1533ІПЗ, 564ІПЗ). Умовно-графічне позначення цих мікросхем показане на мал. 2.33. Як приклад розглянемо AЛП К555ІПЗ.

Ця мікросхема призначена для дії з двома чотирирозрядними двійковими словами: А = А3А2А1 А0 і В = B3 B2B1B0 (мал. 2.33). Конкретний вид операції, який, задається п'ятирозрядним який виконується кодом на входах MS3S2S1 So. Усього цей АЛП здатний виконати 25=32 операції:в залежності від М або 16 логічних (І,І-НІ, ЧИ, АБО-НІ, " Що виключає АБО" і ін.), або 1б арифметичних і арифметико-логічних (додавання, віднімання, подвоєння порівняння чисел і ін.). Операції додавання і віднімання проводяться з прискореним переносом з розряду в розряд. Крім того, мається вхід прийому сигналу переносу С.

|

|

|

Рис. 2.33. Умовне зображення схеми К555 ІП3

На виходах F0F1 F2F3 формуються результати логічних перетворень і арифметичних дій. На виході переносу С4 утвориться сигнал старшого (п'ятого) розряду при виконанні арифметичних операцій. Додаткові виходи - утворення прискореного переносу G і поширення прискореного переносу Р - використовуються тільки при організації багаторозрядних АЛП у випадку їхнього сполучення з блоком прискореного переносу КМ555ІП4.

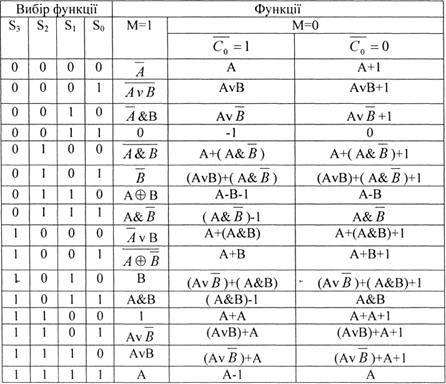

Слова А і В, підлягаючи обробці, можуть бути представлені в озитивній або негативній логіці. Повний перелік операцій, виконуваних AJIП для позитивної логіки, приводиться в табл. 2.15.

Логічні операції виконуються незалежно в кожному розряді. Арифметичні операції виконуються з урахуванням переносів і позик. Обидва типи операцій можуть зустрічатися одночасно. Наприклад, запис (AvB)+(A&B) означає, що спочатку порозрядно виконуються операції інвертування В, логічного додавання (A v В) ілогічного множення А & В, а потім отримані зазначеним чином два чотирирозрядних числа складаються арифметично (з урахуванням переносів).

ПРИКЛАД. Код операції 01010. Операція F=(AvB)+(A&B). Число А= 1001, В=1011. Етапи виконання цієї операції показані на мал. 2.34. Результат операції F=0110.

Таблиця 2.15

При використанні АЛП як компаратора сигнал знімають з виходу А = b (вихід 14) джерела живлення його варто підключати через зовнішній резистор 1 кОм. Режим компаратора забезпечується при М = 0 і S3S2S1 So = 0110. Коли числа А і В рівні, на виході А = В формується сигнал високого рівня. Відсутність колекторного навантаження допускає при коскадуванні АЛП поєднувати виходи А = В за схемою "Монтажне І".

Рис.2.34. Виконання операції MS3 S2 S1 S0 =01010

Згідно табл. 2.16 для визначення співвідношення між

числами А і В у випадку їхньої нерівності використовується

сигнал на виході С4 (висновок 16). Табл. 2.16 складена для

позитивної логіки.

|

|

|

Таблиця 16

| Стан входів | Стан виходу | |

| С | АиВ | |

| А<В | ||

| А<В | ||

| А>В | ||

| А<В |

Для арифметичних дій над словами більшої довжини АЛП включають послідовно (мал. 2.35, а). Тут час підсумовування визначається затримкою поширення сигналу переносу з входу молодшого розряду до виходу з останнього АЛП складає

де tзд.р - затримка поширення сигналу переносу в одному АЛП.

3меншити,час підсумовування можна застосуванням мікросхем К155ІІП4, K533ІП14, 564ІП4, спеціально розроблених для організації прискореного переносу між окремими АЛП а також між групами АЛП- Зі схемою прискореного переносу час підсумовування скорочується приблизно до tзд.р. На мал. 2.35,б показаний 16-розрядний АЛП з блоком прискореного переносу.

Рис. 2.35. 16-розрядний АЛП з послідовним переносом (а) і з блоком прискореного переносу

У випадку нарощування мікросхем прискореного переносу (для чисел, число розрядів яких перевищує 16) використовуються виходи Р і G. За допомогою чотирьох таких мікросхем у сполученні з 16 мікросхемами АЛП можна побудувати 64-розрядний АЛП.

|

|

|

|

|

Дата добавления: 2015-06-27; Просмотров: 1467; Нарушение авторских прав?; Мы поможем в написании вашей работы!