КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Характеристики ПЛИС платформы Virtex-5 ftx

|

|

|

|

Семейство ПЛИС Virtex-5 FXT с встроенным процессорным ядром PowerPC 440

Virtex–5 FXT—платформа в семействе высокопроизводительных FPGA фирмы Xilinx, выполненных с технологическими нормами 65 нм. Начиная с предыдущего поколения FPGA Xilinx использует модульную архитектуру высокопроизводительных FPGA, названную ASMBL (Advanced Silicon Modular Block), что позволило в рамках одного семейства Virtex–4 выпустить сразу три платформы ПЛИС, различавшихся соотношением основных ресурсов — логических ячеек, блоков цифровой обработки, памяти и специализированных модулей (процессорных ядер и высокоскоростных приемопередатчиков). Широкие функциональные возможности в приложениях коммуникации, которые предоставили аппаратные приемопередатчики, привели к тому, что в Virtex–5 такие устройства были размещены и в ПЛИС без аппаратных процессорных ядер — LXT и SXT. Теперь же, правда, с некоторой задержкой относительно выхода предыдущих платформ, появились устройства Virtex–5 FXT, содержащие как приемопередатчики (на что указывает буква T в обозначении), так и аппаратные ядра процессора PowerPC. Характеристики этих ПЛИС приведены в таблице 1. Ячейка Virtex–5 содержит четыре секции, так что для определения количества триггеров и логических генераторов необходимо умножить на 4 количество ячеек, указанное в таблице. Легко заметить, что получающиеся цифры меньше, чем величины, приведенные в обозначении ПЛИС. Это связано с тем, что Xilinx проводит оценку емкости в «стандартных ячейках», содержащих триггер и 4–входовый логический генератор, тогда как в Virtex–5 LUT имеют шесть входов.

Таблица 1. Характеристики ПЛИС новой платформы

| Устройство | Ячеек | DSP48E | Блоков памяти | Итого памяти, кбайт | CMT | PPC | PCI–Express endpoint | Ethernet MAC | Rocket IO GTX |

| XC5VFX30T | |||||||||

| XC5VFX70T | 11 200 | ||||||||

| XC5VFX100T | 16 000 | ||||||||

| XC5VFX130T | 20 480 | 10 728 | |||||||

| XC5VFX200T | 30 720 | 16 416 |

В последней колонке приведено количество скоростных приемопередатчиков Rocket IO GTX, которые отличают данное семейство даже от других платформ Virtex–5 с приемопередатчиками (LXT, SXT). В них используются модули Rocket IO GTP, способные осуществлять обмен данными со скоростями 100–3750 Мбит/с, тогда как у ядер GTX возможные значения скоростей составляют 150–6500 Мбит/с.

|

|

|

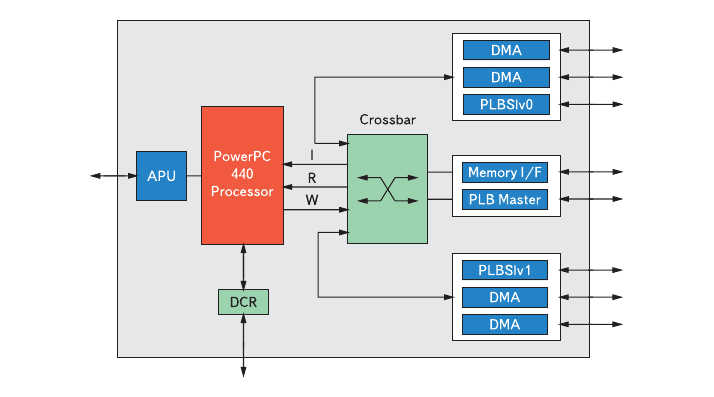

Важной частью таблицы является колонка, обозначенная как PPC. В этой колонке приведено количество процессорных ядер PowerPC 440, которые заменили уже применявшиеся в предыдущих поколениях ПЛИС Xilinx ядра PowerPC 405. Основные сравнительные характеристики этих ядер приведены в таблице 2, а структурное изображение процессорного ядра PowerPC 440 и сопутствующих элементов показано на рис. 1.

Таблица 2. Основные сравнительные характеристики новых ядер

| PowerPC 405 | PowerPC 440 | |

| Конвейер, стадий | 7, out–of–order | |

| Тактовая частота, МГц | ||

| Максимальная производительность, DMIPS | ||

| Кэш инструкций/данных | 16/16 кбайт, 2–way | 32/32 кбайт, 64–way |

Рис. 1. Блок процессора PowerPC 440, встраиваемый в ПЛИС Virtex–5 FXT

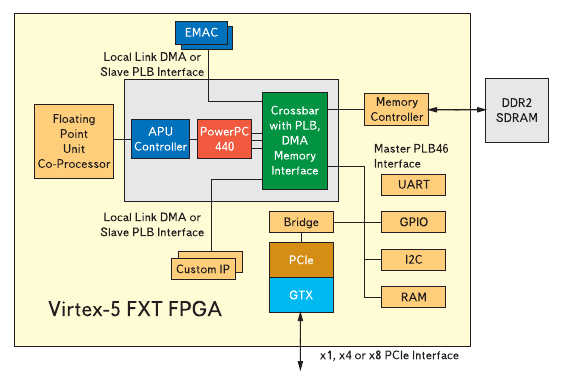

На рис. 1 можно видеть, что обмен данными с основными накристальными устройствами происходит через устройство коммутации (crossbar). Это устройство позволяет разгрузить основную шину процессора PLB, поскольку к ней в проектах на базе ПЛИС оказываются подключенными сразу несколько устройств с большим трафиком. Например, при одновременном подключении высокоскоростной внешней памяти и контроллера Ethernet каждое из этих устройств само по себе обладает неплохими характеристиками, но их присутствие на одной и той же шине сразу снижает максимальные скорости обмена данными. Пример системы, использующей несколько скоростных интерфейсов, показан на рис. 2. На нем можно видеть, что такие требовательные к ресурсам системной шины устройства, как внешняя память, EMAC, PCIe, имеют собственные подключения к коммутатору, что позволяет перераспределять потоки данных (например, выполнять прямой доступ в память, как показано на рис.3).

|

|

|

Рис.3

Лекция 16 Stratix III – новое семейство FPGA фирмы Altera

Проекты, в которых используются микросхемы программируемой логики, становятся все более сложными. С одной стороны, это требует от разработчиков повышения квалификации и может приводить к затягиванию разработок. С другой стороны, современные условия рынка предполагают сокращение времени разработки и себестоимости разрабатываемых устройств. Для преодоления этого противоречия фирмы-производители ПЛИС предлагают как усовершенствованные средства разработки, так и новые семейства микросхем программируемой логики. Одним из новейших высокопроизводительных семейств FPGA, анонсированных фирмой Altera, является Stratix III.

Новое семейство FPGA — Stratix III — сочетает высокую производительность, большой логический объем и малое энергопотребление.

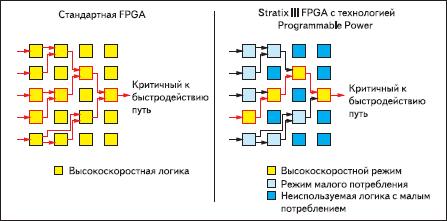

Главная особенность Stratix III — сниженное до двух раз энергопотребление (как динамическое, так и статическое) по сравнению с семействами FPGA предыдущего поколения, без потери производительности. Этого удалось достигнуть за счет реализации технологии программируемого энергопотребления (Programmable Power Technology), которая позволяет конфигурировать ресурсы ПЛИС (логические блоки, блоки цифровой обработки, блоки памяти) либо в режим с высокой производительностью, либо в режим с пониженным энергопотреблением. Предлагаемые фирмой Altera средства разработок предоставляют возможность анализировать проект и определять, какая производительность необходима тому или иному блоку. Блоки, не требующие высокой производительности (в том числе и неиспользуемые в проекте), устанавливаются в режим пониженного энергопотребления. Блоки, функционирование которых критично ко времени, устанавливаются в высокоскоростной режим. Таким образом, технология программируемого энергопотребления позволяет совместить в одном проекте два до сих пор не совместимых требования. Возможность устанавливать блоки ПЛИС либо в высокоскоростной режим, либо в режим с низким энергопотреблением, — новое слово в мире программируемой логики (рис. 1).

|

|

|

Рис. 1. Использование различных режимов блоков Stratix III по сравнению с FPGA предыдущего поколения

Другая особенность семейства Stratix III, способная снизить энергопотребление, — возможность выбора напряжения питания ядра (VCCint). Для проектов, где определяющим фактором является высокая производительность, используется напряжение питания ядра 1,1 В. Для проектов, требующих пониженного энергопотребления, — 0,9 В.

Микросхемы Stratix III будут выпускаться по 65-нанометровой технологии. Внутренние тактовые частоты Stratix III могут достигать 600 МГц. Максимальная производительность FPGA Stratix III на 25% выше, чем у семейств ПЛИС предыдущего поколения.

Семейство Stratix III разделено на три подсемейства, каждое из них оптимизировано для определенных приложений:

- Stratix III L — для решения задач, где требуется большая логическая емкость;

- Stratix III E — для решения задач цифровой обработки сигналов и задач, требующих применения больших объемов памяти;

- Stratix III GX — для решения задач высокоскоростных коммуникаций (микросхемы данного подсемейства будут содержать мультигигабитные трансиверы).

Выпуск первых инженерных образцов FPGA семейства Stratix III планируется в III квартале 2007 года. Подробная информация по семейству Stratix III (в том числе и предварительное техническое описание) доступна на сайте Altera www.altera.com/stratix3.

|

|

|

|

|

Дата добавления: 2014-01-07; Просмотров: 593; Нарушение авторских прав?; Мы поможем в написании вашей работы!